# **Technical Reference Guide**

For the

Compaq Deskpro EX/EXS Series of Personal Computers

Covering Models Featuring

Intel Celeron and Pentium III Processors

And the

**Intel 815 Chipset**

**COMPAQ**

This document is designed to allow printing as an 8 ½ x 11-inch hardcopy that will fit into a standard 3-ring binder. Provided below is a title block that can be copied and/or cut out and placed into a slip or taped onto the edge of the binder.

**COMPAQ.** Deskpro EX Series Personal Computers

Featuring Intel Celeron and Pentium III Processors and the Intel 815 Chipset

**TRG**

| Reader Feedback                                                                                                                              |  |

|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| Please feel free to send any questions, suggestions, corrections, or comments regarding this document please to the following email address: |  |

| Desktop.training.feedback@Compaq.com                                                                                                         |  |

| When responding, please state the title and edition of the referenced document.                                                              |  |

|                                                                                                                                              |  |

|                                                                                                                                              |  |

|                                                                                                                                              |  |

|                                                                                                                                              |  |

|                                                                                                                                              |  |

### NOTICE

The information in this document is subject to change without notice.

COMPAQ COMPUTER CORPORATION SHALL NOT BE LIABLE FOR TECHNICAL OR EDITORIAL ERRORS OR OMISSIONS HEREIN; NOR FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES RESULTING FROM THE FURNISHING, PERFORMANCE, OR USE OF THIS MATERIAL. IT IS THE RESPONSIBILITY OF MANUFACTURERS TO ENSURE THAT DEVICES DESIGNED TO BE USED WITH COMPAQ PRODUCTS COMPLY WITH FCC CLASS B EMISSIONS REQUIREMENTS.

This guide contains information protected by copyright. Except for use in connection with the described Compaq product, no part of this document may be photocopied or reproduced in any form without prior written consent from Compaq Computer Corporation.

©2000 Compaq Computer Corporation All rights reserved. Published in the USA

Compaq, Deskpro, LTE, Contura, Presario, ProLinea Registered U.S. Patent and Trademark Office

Product names mentioned in this document may be trademarks and/or registered trademarks of other companies.

"Celeron," "Pentium" and "MMX" are registered trademarks of Intel Corporation. "Microsoft," "MS-DOS," "Windows," and "Windows NT" are registered trademarks of Microsoft Corporation.

For more information regarding specifications and Compaq-specific parts please contact Compaq Computer Corporation.

Technical Reference Guide for Compaq Deskpro EX Series Personal Computers First Edition - August 2000 Document Number 137H-0800A-WWEN

Compaq Deskpro EX Series of Personal Computers

# TABLE OF CONTENTS

| 1.1       ABOUT THIS GUIDE       1-1         1.1.1       USING THIS GUIDE       1-1         1.1.2       ADDITIONAL INFORMATION SOURCES       1-1         1.2       MODEL NUMBERING CONVENTION       1-1         1.3       NOTATIONAL CONVENTIONS       1-2         1.3.1       VALUES       1-2         1.3.2       RANGES       1-2         1.3.3       SIGNAL LABELS       1-2         1.3.4       REGISTER NOTATION AND USAGE       1-2         1.3.5       BIT NOTATION       1-2         1.4       COMMON ACRONYMS AND ABBREVIATIONS       1-3         CHAPTER 2 SYSTEM OVERVIEW         2.1       INTRODUCTION       2-1         2.2       FEATURES AND OPTIONS       2-2         2.2.1       STANDARD FEATURES       2-2         2.2.2       OPTIONS       2-3         2.3       MECHANICAL DESIGN       2-4         2.3.1       CABINET LAYOUTS       2-5         2.3.2       CHASSIS LAYOUTS       2-5         2.3.2       CHASSIS LAYOUTS       2-5         2.3.2       SUBSIS MARCHITECTURE       2-10         2.4.1       PROCESSORS       2-12         2.4.2       CHIP     | CHAPTER 1 INTRODUCTION                |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------|

| 1.1.1   USING THIS GUIDE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1.1 ABOUT THIS GUIDE                  | 1-1  |

| 1.1.2   ADDITIONAL INFORMATION SOURCES   1-1   1.2   MODEL NUMBERING CONVENTION   1-1   1.3   NOTATIONAL CONVENTIONS   1-2   1.3.1   VALUES   1-2   1.3.2   RANGES   1-2   1.3.3   SIGNAL LABELS   1-2   1.3.4   REGISTER NOTATION AND USAGE   1-2   1.3.5   BIT NOTATION   1-2   1.4   COMMON ACRONYMS AND ABBREVIATIONS   1-3    CHAPTER 2 SYSTEM OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |      |

| 1.3 NOTATIONAL CONVENTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       |      |

| 1.3 NOTATIONAL CONVENTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       |      |

| 1.3.1       VALUES       1-2         1.3.2       RANGES       1-2         1.3.3       SIGNAL LABELS       1-2         1.3.4       REGISTER NOTATION AND USAGE       1-2         1.3.5       BIT NOTATION       1-2         1.4       COMMON ACRONYMS AND ABBREVIATIONS       1-3         CHAPTER 2 SYSTEM OVERVIEW         CHAPTER 2 SYSTEM OVERVIEW         2.1       INTRODUCTION       2-1         2.2       FEATURES AND OPTIONS       2-2         2.2.1       STANDARD FEATURES       2-2         2.2.2       OPTIONS       2-3         2.3       MECHANICAL DESIGN       2-4         2.3.1       CABINET LAYOUTS       2-5         2.3.2       CHASSIS LAYOUTS       2-5         2.3.3       BOARD LAYOUT       2-9         2.4       SYSTEM ARCHITECTURE       2-10         2.4.1       PROCESSORS       2-12         2.4.2       CHIPSET       2-14         2.4.3       SUPPORT COMPONENTS       2-14         2.4.4       SYSTEM MEMORY       2-15         2.4.5       MASS STORAGE       2-15         2.4.6       SERIAL AND PARALLEL INTERFACES       2-15 <td></td> <td></td> |                                       |      |

| 1.3.2       RANGES.       1-2         1.3.3       SIGNAL LABELS.       1-2         1.3.4       REGISTER NOTATION AND USAGE       1-2         1.3.5       BIT NOTATION       1-2         1.4       COMMON ACRONYMS AND ABBREVIATIONS       1-3         CHAPTER 2 SYSTEM OVERVIEW         2.1       INTRODUCTION       2-1         2.2       FEATURES AND OPTIONS       2-2         2.2.1       STANDARD FEATURES       2-2         2.2.2       OPTIONS       2-3         2.3       MECHANICAL DESIGN       2-4         2.3.1       CABINET LAYOUTS       2-5         2.3.2       CHASSIS LAYOUTS       2-7         2.3.3       BOARD LAYOUT       2-9         2.4       SYSTEM ARCHITECTURE       2-10         2.4.1       PROCESSORS       2-12         2.4.2       CHIPSET       2-14         2.4.3       SUPPORT COMPONENTS       2-14         2.4.4       SYSTEM MEMORY       2-15         2.4.5       MASS STORAGE       2-15         2.4.6       SERIAL AND PARALLEL INTERFACE       2-15         2.4.7       UNIVERSAL SERIAL BUS INTERFACE       2-15         2.4.9       AUD     |                                       |      |

| 1.3.4       REGISTER NOTATION       1-2         1.3.5       BIT NOTATION       1-2         1.4       COMMON ACRONYMS AND ABBREVIATIONS       1-3         CHAPTER 2 SYSTEM OVERVIEW         2.1       INTRODUCTION       2-1         2.2       FEATURES AND OPTIONS       2-2         2.2.1       STANDARD FEATURES       2-2         2.2.2       OPTIONS       2-3         2.3       MECHANICAL DESIGN       2-4         2.3.1       CABINET LAYOUTS       2-5         2.3.2       CHASSIS LAYOUTS       2-7         2.3.3       BOARD LAYOUT       2-9         2.4       SYSTEM ARCHITECTURE       2-10         2.4.1       PROCESSORS       2-12         2.4.2       CHIPSET       2-14         2.4.3       SUPPORT COMPONENTS       2-14         2.4.4       SYSTEM MEMORY       2-15         2.4.5       MASS STORAGE       2-15         2.4.6       SERIAL AND PARALLEL INTERFACES       2-15         2.4.7       UNIVERSAL SERIAL BUS INTERFACE       2-15         2.4.8       GRAPHICS SUBSYSTEM       2-16         2.4.9       AUDIO SUBSYSTEM       2-17         2.5            | 1.3.2 RANGES                          | 1-2  |

| 1.3.5 BIT NOTATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.3.3 SIGNAL LABELS                   | 1-2  |

| 1.4       COMMON ACRONYMS AND ABBREVIATIONS       1-3         CHAPTER 2 SYSTEM OVERVIEW         2.1       INTRODUCTION       2-1         2.2       FEATURES AND OPTIONS       2-2         2.2.1       STANDARD FEATURES       2-2         2.2.2       OPTIONS       2-3         2.3       MECHANICAL DESIGN       2-4         2.3.1       CABINET LAYOUTS       2-5         2.3.2       CHASSIS LAYOUTS       2-7         2.3.3       BOARD LAYOUT       2-9         2.4       SYSTEM ARCHITECTURE       2-10         2.4.1       PROCESSORS       2-12         2.4.2       CHIPSET       2-14         2.4.3       SUPPORT COMPONENTS       2-14         2.4.4       SYSTEM MEMORY       2-14         2.4.5       MASS STORAGE       2-15         2.4.6       SERIAL AND PARALLEL INTERFACES       2-15         2.4.7       UNIVERSAL SERIAL BUS INTERFACE       2-15         2.4.9       AUDIO SUBSYSTEM       2-16         2.4.9       A UDIO SUBSYSTEM       2-17         2.5       SPECIFICATIONS       2-17         3.1       INTRODUCTION       3-1         3.2       PROCESSO     | 1.3.4 REGISTER NOTATION AND USAGE     | 1-2  |

| CHAPTER 2 SYSTEM OVERVIEW         2.1       INTRODUCTION       2-1         2.2       FEATURES AND OPTIONS       2-2         2.2.1       STANDARD FEATURES       2-2         2.2.2       OPTIONS       2-3         2.3       MECHANICAL DESIGN       2-4         2.3.1       CABINET LAYOUTS       2-5         2.3.2       CHASSIS LAYOUTS       2-7         2.3.3       BOARD LAYOUT       2-9         2.4       SYSTEM ARCHITECTURE       2-10         2.4.1       PROCESSORS       2-12         2.4.2       CHIPSET       2-14         2.4.3       SUPPORT COMPONENTS       2-14         2.4.4       SYSTEM MEMORY       2-15         2.4.5       MASS STORAGE       2-15         2.4.6       SERIAL AND PARALLEL INTERFACES       2-15         2.4.6       SERIAL AND PARALLEL INTERFACES       2-15         2.4.9       AUDIO SUBSYSTEM       2-16         2.4.9       AUDIO SUBSYSTEM       2-17         2.5       SPECIFICATIONS       2-17         2.5       SPECIFICATIONS       3-2         3.2       PROCESSOR       3-2         3.2.1       CELERON PROCESSOR                 | 1.3.5 BIT NOTATION                    | 1-2  |

| 2.1       INTRODUCTION       2-1         2.2       FEATURES AND OPTIONS       2-2         2.2.1       STANDARD FEATURES       2-2         2.2.2       OPTIONS       2-3         2.3       MECHANICAL DESIGN       2-4         2.3.1       CABINET LAYOUTS       2-5         2.3.2       CHASSIS LAYOUTS       2-7         2.3.3       BOARD LAYOUT       2-9         2.4       SYSTEM ARCHITECTURE       2-10         2.4.1       PROCESSORS       2-12         2.4.2       CHIPSET       2-14         2.4.3       SUPPORT COMPONENTS       2-14         2.4.4       SYSTEM MEMORY       2-15         2.4.5       MASS STORAGE       2-15         2.4.6       SERIAL AND PARALLEL INTERFACES       2-15         2.4.7       UNIVERSAL SERIAL BUS INTERFACE       2-15         2.4.8       GRAPHICS SUBSYSTEM       2-16         2.4.9       AUDIO SUBSYSTEM       2-17         2.5       SPECIFICATIONS       2-17         3.1       INTRODUCTION       3-1         3.2       PROCESSOR       3-2         3.2.1       CELERON PROCESSOR       3-2         3.2.2       PENTIUM            | 1.4 COMMON ACRONYMS AND ABBREVIATIONS | 1-3  |

| 2.2       FEATURES AND OPTIONS       2-2         2.2.1       STANDARD FEATURES       2-2         2.2.2       OPTIONS       2-3         2.3       MECHANICAL DESIGN       2-4         2.3.1       CABINET LAYOUTS       2-5         2.3.2       CHASSIS LAYOUTS       2-7         2.3.3       BOARD LAYOUT       2-9         2.4       SYSTEM ARCHITECTURE       2-10         2.4.1       PROCESSORS       2-12         2.4.2       CHIPSET       2-14         2.4.3       SUPPORT COMPONENTS       2-14         2.4.4       SYSTEM MEMORY       2-15         2.4.5       MASS STORAGE       2-15         2.4.6       SERIAL AND PARALLEL INTERFACES       2-15         2.4.7       UNIVERSAL SERIAL BUS INTERFACE       2-15         2.4.8       GRAPHICS SUBSYSTEM       2-16         2.4.9       AUDIO SUBSYSTEM       2-17         2.5       SPECIFICATIONS       2-17         3.1       INTRODUCTION       3-1         3.2       PROCESSOR       3-2         3.2.1       CELERON PROCESSOR       3-2         3.2.2       PENTIUM III PROCESSOR       3-3         3.2.3       <       | CHAPTER 2 SYSTEM OVERVIEW             |      |

| 2.2       FEATURES AND OPTIONS       2-2         2.2.1       STANDARD FEATURES       2-2         2.2.2       OPTIONS       2-3         2.3       MECHANICAL DESIGN       2-4         2.3.1       CABINET LAYOUTS       2-5         2.3.2       CHASSIS LAYOUTS       2-7         2.3.3       BOARD LAYOUT       2-9         2.4       SYSTEM ARCHITECTURE       2-10         2.4.1       PROCESSORS       2-12         2.4.2       CHIPSET       2-14         2.4.3       SUPPORT COMPONENTS       2-14         2.4.4       SYSTEM MEMORY       2-15         2.4.5       MASS STORAGE       2-15         2.4.6       SERIAL AND PARALLEL INTERFACES       2-15         2.4.7       UNIVERSAL SERIAL BUS INTERFACE       2-15         2.4.8       GRAPHICS SUBSYSTEM       2-16         2.4.9       AUDIO SUBSYSTEM       2-17         2.5       SPECIFICATIONS       2-17         3.1       INTRODUCTION       3-1         3.2       PROCESSOR       3-2         3.2.1       CELERON PROCESSOR       3-2         3.2.2       PENTIUM III PROCESSOR       3-3         3.2.3       <       | 2.1 INTRODUCTION                      | 2-1  |

| 2.2.1       STANDARD FEATURES       2-2         2.2.2       OPTIONS       2-3         2.3       MECHANICAL DESIGN       2-4         2.3.1       CABINET LAYOUTS       2-5         2.3.2       CHASSIS LAYOUTS       2-7         2.3.3       BOARD LAYOUT       2-9         2.4       SYSTEM ARCHITECTURE       2-10         2.4.1       PROCESSORS       2-12         2.4.2       CHIPSET       2-14         2.4.3       SUPPORT COMPONENTS       2-14         2.4.4       SYSTEM MEMORY       2-15         2.4.5       MASS STORAGE       2-15         2.4.6       SERIAL AND PARALLEL INTERFACES       2-15         2.4.7       UNIVERSAL SERIAL BUS INTERFACE       2-15         2.4.8       GRAPHICS SUBSYSTEM       2-16         2.4.9       AUDIO SUBSYSTEM       2-17         2.5       SPECIFICATIONS       2-17         CHAPTER 3 PROCESSOR/MEMORY SUBSYSTEM         3.1       INTRODUCTION       3-1         3.2       PROCESSOR       3-2         3.2.1       CELERON PROCESSOR       3-2         3.2.2       PENTIUM III PROCESSOR       3-3         3.2.3       PROCESS     |                                       |      |

| 2.2.2       OPTIONS       2-3         2.3       MECHANICAL DESIGN       2-4         2.3.1       CABINET LAYOUTS       2-5         2.3.2       CHASSIS LAYOUTS       2-7         2.3.3       BOARD LAYOUT       2-9         2.4       SYSTEM ARCHITECTURE       2-10         2.4.1       PROCESSORS       2-12         2.4.2       CHIPSET       2-14         2.4.3       SUPPORT COMPONENTS       2-14         2.4.4       SYSTEM MEMORY       2-15         2.4.5       MASS STORAGE       2-15         2.4.6       SERIAL AND PARALLEL INTERFACES       2-15         2.4.7       UNIVERSAL SERIAL BUS INTERFACE       2-15         2.4.8       GRAPHICS SUBSYSTEM       2-16         2.4.9       AUDIO SUBSYSTEM       2-16         2.4.9       AUDIO SUBSYSTEM       2-17         2.5       SPECIFICATIONS       2-17         CHAPTER 3 PROCESSOR/MEMORY SUBSYSTEM         3.1       INTRODUCTION       3-1         3.2       PROCESSOR       3-2         3.2.1       CELERON PROCESSOR       3-2         3.2.2       PENTIUM III PROCESSOR       3-3         3.2.3       PROCESSO     |                                       |      |

| 2.3       MECHANICAL DESIGN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                       |      |

| 2.3.1       CABINET LAYOUTS       2-5         2.3.2       CHASSIS LAYOUTS       2-7         2.3.3       BOARD LAYOUT       2-9         2.4       SYSTEM ARCHITECTURE       2-10         2.4.1       PROCESSORS       2-12         2.4.2       CHIPSET       2-14         2.4.3       SUPPORT COMPONENTS       2-14         2.4.4       SYSTEM MEMORY       2-15         2.4.5       MASS STORAGE       2-15         2.4.6       SERIAL AND PARALLEL INTERFACES       2-15         2.4.7       UNIVERSAL SERIAL BUS INTERFACE       2-15         2.4.8       GRAPHICS SUBSYSTEM       2-16         2.4.9       AUDIO SUBSYSTEM       2-17         2.5       SPECIFICATIONS       2-17         CHAPTER 3 PROCESSOR/MEMORY SUBSYSTEM         3.1       INTRODUCTION       3-1         3.2       PROCESSOR       3-2         3.2.1       CELERON PROCESSOR       3-2         3.2.1       CELERON PROCESSOR       3-2         3.2.2       PENTIUM III PROCESSOR       3-3         3.2.3       PROCESSOR UPGRADING       3-4         3.3       MEMORY SUBSYSTEM       3-5                      |                                       |      |

| 2.3.3       BOARD LAYOUT       2-9         2.4       SYSTEM ARCHITECTURE       2-10         2.4.1       PROCESSORS       2-12         2.4.2       CHIPSET       2-14         2.4.3       SUPPORT COMPONENTS       2-14         2.4.4       SYSTEM MEMORY       2-15         2.4.5       MASS STORAGE       2-15         2.4.6       SERIAL AND PARALLEL INTERFACES       2-15         2.4.7       UNIVERSAL SERIAL BUS INTERFACE       2-15         2.4.8       GRAPHICS SUBSYSTEM       2-16         2.4.9       AUDIO SUBSYSTEM       2-17         2.5       SPECIFICATIONS       2-17         CHAPTER 3 PROCESSOR/MEMORY SUBSYSTEM         3.1       INTRODUCTION       3-1         3.2       PROCESSOR       3-2         3.2.1       CELERON PROCESSOR       3-2         3.2.2       PENTIUM III PROCESSOR       3-3         3.2.3       PROCESSOR UPGRADING       3-4         3.3       MEMORY SUBSYSTEM       3-5                                                                                                                                                                  |                                       |      |

| 2.4       SYSTEM ARCHITECTURE       2-10         2.4.1       PROCESSORS       2-12         2.4.2       CHIPSET       2-14         2.4.3       SUPPORT COMPONENTS       2-14         2.4.4       SYSTEM MEMORY       2-15         2.4.5       MASS STORAGE       2-15         2.4.6       SERIAL AND PARALLEL INTERFACES       2-15         2.4.7       UNIVERSAL SERIAL BUS INTERFACE       2-15         2.4.8       GRAPHICS SUBSYSTEM       2-16         2.4.9       AUDIO SUBSYSTEM       2-17         2.5       SPECIFICATIONS       2-17         CHAPTER 3 PROCESSOR/MEMORY SUBSYSTEM         3.1       INTRODUCTION       3-1         3.2       PROCESSOR       3-2         3.2.1       CELERON PROCESSOR       3-2         3.2.2       PENTIUM III PROCESSOR       3-3         3.2.3       PROCESSOR UPGRADING       3-4         3.3       MEMORY SUBSYSTEM       3-5                                                                                                                                                                                                             | 2.3.2 CHASSIS LAYOUTS                 | 2-7  |

| 2.4.1       PROCESSORS       2-12         2.4.2       CHIPSET       2-14         2.4.3       SUPPORT COMPONENTS       2-14         2.4.4       SYSTEM MEMORY       2-15         2.4.5       MASS STORAGE       2-15         2.4.6       SERIAL AND PARALLEL INTERFACES       2-15         2.4.7       UNIVERSAL SERIAL BUS INTERFACE       2-15         2.4.8       GRAPHICS SUBSYSTEM       2-16         2.4.9       AUDIO SUBSYSTEM       2-17         2.5       SPECIFICATIONS       2-17         CHAPTER 3 PROCESSOR/MEMORY SUBSYSTEM         3.1       INTRODUCTION       3-1         3.2       PROCESSOR       3-2         3.2.1       CELERON PROCESSOR       3-2         3.2.2       PENTIUM III PROCESSOR       3-3         3.2.3       PROCESSOR UPGRADING       3-4         3.3       MEMORY SUBSYSTEM       3-5                                                                                                                                                                                                                                                              | 2.3.3 BOARD LAYOUT                    | 2-9  |

| 2.4.2       CHIPSET       2-14         2.4.3       SUPPORT COMPONENTS       2-14         2.4.4       SYSTEM MEMORY       2-15         2.4.5       MASS STORAGE       2-15         2.4.6       SERIAL AND PARALLEL INTERFACES       2-15         2.4.7       UNIVERSAL SERIAL BUS INTERFACE       2-15         2.4.8       GRAPHICS SUBSYSTEM       2-16         2.4.9       AUDIO SUBSYSTEM       2-17         2.5       SPECIFICATIONS       2-17         CHAPTER 3 PROCESSOR/MEMORY SUBSYSTEM         3.1       INTRODUCTION       3-1         3.2       PROCESSOR       3-2         3.2.1       CELERON PROCESSOR       3-2         3.2.1       CELERON PROCESSOR       3-2         3.2.2       PENTIUM III PROCESSOR       3-3         3.2.3       PROCESSOR UPGRADING       3-4         3.3       MEMORY SUBSYSTEM       3-5                                                                                                                                                                                                                                                        | 2.4 SYSTEM ARCHITECTURE               | 2-10 |

| 2.4.3       SUPPORT COMPONENTS       2-14         2.4.4       SYSTEM MEMORY       2-15         2.4.5       MASS STORAGE       2-15         2.4.6       SERIAL AND PARALLEL INTERFACES       2-15         2.4.7       UNIVERSAL SERIAL BUS INTERFACE       2-15         2.4.8       GRAPHICS SUBSYSTEM       2-16         2.4.9       AUDIO SUBSYSTEM       2-17         2.5       SPECIFICATIONS       2-17         CHAPTER 3 PROCESSOR/MEMORY SUBSYSTEM         3.1       INTRODUCTION       3-1         3.2       PROCESSOR       3-2         3.2.1       CELERON PROCESSOR       3-2         3.2.2       PENTIUM III PROCESSOR       3-3         3.2.3       PROCESSOR UPGRADING       3-4         3.3       MEMORY SUBSYSTEM       3-5                                                                                                                                                                                                                                                                                                                                               | 2.4.1 PROCESSORS                      | 2-12 |

| 2.4.4       SYSTEM MEMORY       2-15         2.4.5       MASS STORAGE       2-15         2.4.6       SERIAL AND PARALLEL INTERFACES       2-15         2.4.7       UNIVERSAL SERIAL BUS INTERFACE       2-15         2.4.8       GRAPHICS SUBSYSTEM       2-16         2.4.9       AUDIO SUBSYSTEM       2-17         2.5       SPECIFICATIONS       2-17         CHAPTER 3 PROCESSOR/MEMORY SUBSYSTEM         3.1       INTRODUCTION       3-1         3.2       PROCESSOR       3-2         3.2.1       CELERON PROCESSOR       3-2         3.2.2       PENTIUM III PROCESSOR       3-3         3.2.3       PROCESSOR UPGRADING       3-4         3.3       MEMORY SUBSYSTEM       3-5                                                                                                                                                                                                                                                                                                                                                                                                 | 2.4.2 CHIPSET                         | 2-14 |

| 2.4.5       MASS STORAGE       2-15         2.4.6       SERIAL AND PARALLEL INTERFACES       2-15         2.4.7       UNIVERSAL SERIAL BUS INTERFACE       2-15         2.4.8       GRAPHICS SUBSYSTEM       2-16         2.4.9       AUDIO SUBSYSTEM       2-17         2.5       SPECIFICATIONS       2-17         CHAPTER 3 PROCESSOR/MEMORY SUBSYSTEM         3.1       INTRODUCTION       3-1         3.2       PROCESSOR       3-2         3.2.1       CELERON PROCESSOR       3-2         3.2.2       PENTIUM III PROCESSOR       3-3         3.2.3       PROCESSOR UPGRADING       3-4         3.3       MEMORY SUBSYSTEM       3-5                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2.4.3 SUPPORT COMPONENTS              | 2-14 |

| 2.4.6       SERIAL AND PARALLEL INTERFACES       2-15         2.4.7       UNIVERSAL SERIAL BUS INTERFACE       2-15         2.4.8       GRAPHICS SUBSYSTEM       2-16         2.4.9       AUDIO SUBSYSTEM       2-17         2.5       SPECIFICATIONS       2-17         CHAPTER 3 PROCESSOR/MEMORY SUBSYSTEM         3.1       INTRODUCTION       3-1         3.2       PROCESSOR       3-2         3.2.1       CELERON PROCESSOR       3-2         3.2.2       PENTIUM III PROCESSOR       3-3         3.2.3       PROCESSOR UPGRADING       3-4         3.3       MEMORY SUBSYSTEM       3-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2.4.4 SYSTEM MEMORY                   | 2-15 |

| 2.4.7       UNIVERSAL SERIAL BUS INTERFACE       2-15         2.4.8       GRAPHICS SUBSYSTEM       2-16         2.4.9       AUDIO SUBSYSTEM       2-17         2.5       SPECIFICATIONS       2-17         CHAPTER 3 PROCESSOR/MEMORY SUBSYSTEM         3.1       INTRODUCTION       3-1         3.2       PROCESSOR       3-2         3.2.1       CELERON PROCESSOR       3-2         3.2.2       PENTIUM III PROCESSOR       3-3         3.2.3       PROCESSOR UPGRADING       3-4         3.3       MEMORY SUBSYSTEM       3-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.4.5 MASS STORAGE                    | 2-15 |

| 2.4.8 GRAPHICS SUBSYSTEM       2-16         2.4.9 AUDIO SUBSYSTEM       2-17         2.5 SPECIFICATIONS       2-17         CHAPTER 3 PROCESSOR/MEMORY SUBSYSTEM         3.1 INTRODUCTION       3-1         3.2 PROCESSOR       3-2         3.2.1 CELERON PROCESSOR       3-2         3.2.2 PENTIUM III PROCESSOR       3-3         3.2.3 PROCESSOR UPGRADING       3-4         3.3 MEMORY SUBSYSTEM       3-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.4.6 SERIAL AND PARALLEL INTERFACES  | 2-15 |

| 2.4.9 AUDIO SUBSYSTEM       2-17         2.5 SPECIFICATIONS       2-17         CHAPTER 3 PROCESSOR/MEMORY SUBSYSTEM         3.1 INTRODUCTION       3-1         3.2 PROCESSOR       3-2         3.2.1 CELERON PROCESSOR       3-2         3.2.2 PENTIUM III PROCESSOR       3-3         3.2.3 PROCESSOR UPGRADING       3-4         3.3 MEMORY SUBSYSTEM       3-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.4.7 UNIVERSAL SERIAL BUS INTERFACE  | 2-15 |

| 2.5       SPECIFICATIONS       2-17         CHAPTER 3 PROCESSOR/MEMORY SUBSYSTEM         3.1       INTRODUCTION       3-1         3.2       PROCESSOR       3-2         3.2.1       CELERON PROCESSOR       3-2         3.2.2       PENTIUM III PROCESSOR       3-3         3.2.3       PROCESSOR UPGRADING       3-4         3.3       MEMORY SUBSYSTEM       3-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                       |      |

| CHAPTER 3 PROCESSOR/MEMORY SUBSYSTEM         3.1 INTRODUCTION       3-1         3.2 PROCESSOR       3-2         3.2.1 CELERON PROCESSOR       3-2         3.2.2 PENTIUM III PROCESSOR       3-3         3.2.3 PROCESSOR UPGRADING       3-4         3.3 MEMORY SUBSYSTEM       3-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.4.9 AUDIO SUBSYSTEM                 | 2-17 |

| 3.1       INTRODUCTION       3-1         3.2       PROCESSOR       3-2         3.2.1       CELERON PROCESSOR       3-2         3.2.2       PENTIUM III PROCESSOR       3-3         3.2.3       PROCESSOR UPGRADING       3-4         3.3       MEMORY SUBSYSTEM       3-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.5 SPECIFICATIONS                    | 2-17 |

| 3.1       INTRODUCTION       3-1         3.2       PROCESSOR       3-2         3.2.1       CELERON PROCESSOR       3-2         3.2.2       PENTIUM III PROCESSOR       3-3         3.2.3       PROCESSOR UPGRADING       3-4         3.3       MEMORY SUBSYSTEM       3-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CHAPTER 3 PROCESSOR/MEMORY SUBSYSTEM  |      |

| 3.2       PROCESSOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       |      |

| 3.2.1       CELERON PROCESSOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                       |      |

| 3.2.2PENTIUM III PROCESSOR3-33.2.3PROCESSOR UPGRADING3-43.3MEMORY SUBSYSTEM3-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                       |      |

| 3.2.3 PROCESSOR UPGRADING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       |      |

| 3.3 MEMORY SUBSYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                       |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       |      |

| CHAPTI | ER 4 SYSTEM SUPPORT                      | ••••• |

|--------|------------------------------------------|-------|

| 4.1    | INTRODUCTION                             | 4-1   |

| 4.2    | PCI BUS OVERVIEW                         |       |

| 4.2.1  | PCI BUS TRANSACTIONS                     | 4-3   |

| 4.2.2  | PCI BUS MASTER ARBITRATION               | 4-6   |

| 4.2.3  | 3 OPTION ROM MAPPING                     | 4-7   |

| 4.2.4  |                                          |       |

| 4.2.5  | 5 PCI POWER MANAGEMENT SUPPORT           | 4-7   |

| 4.2.6  | 6 PCI SUB-BUSSES                         | 4-7   |

| 4.2.7  | 7 PCI CONFIGURATION                      | 4-8   |

| 4.2.8  | 8 PCI CONNECTOR                          | 4-9   |

| 4.3    | AGP BUS OVERVIEW                         | 4-10  |

| 4.3.1  |                                          |       |

| 4.3.2  |                                          |       |

| 4.3.3  |                                          |       |

| 4.4    |                                          |       |

| 4.4.   |                                          |       |

| 4.4.2  |                                          |       |

| 4.5    | SYSTEM CLOCK DISTRIBUTION                |       |

| 4.6    | REAL-TIME CLOCK AND CONFIGURATION MEMORY |       |

| 4.6.   |                                          |       |

| 4.6.2  |                                          |       |

| 4.6.3  |                                          |       |

| 4.7    | SYSTEM MANAGEMENT                        |       |

| 4.7.1  |                                          |       |

| 4.7.2  |                                          |       |

| 4.7.3  |                                          |       |

| 4.7.4  |                                          |       |

| 4.8    | SYSTEM COOLING                           |       |

|        | REGISTER MAP AND MISCELLANEOUS FUNCTIONS |       |

| 4.9.1  |                                          |       |

| 4.9.2  |                                          |       |

| 4.9.3  | 3 LPC47B357 I/O CONTROLLER FUNCTIONS     | 4-40  |

|        |                                          |       |

|        |                                          |       |

| CHAPTI | ER 5 INPUT/OUTPUT INTERFACES             | ••••• |

| 5.1    | INTRODUCTION                             | 5-1   |

|        | ENHANCED IDE INTERFACE                   |       |

| 5.2.1  | 1 IDE PROGRAMMING                        | 5-1   |

| 5.2.2  | 2 IDE CONNECTOR                          | 5-3   |

| 5.3    | DISKETTE DRIVE INTERFACE                 |       |

| 5.3.1  | 1 DISKETTE DRIVE PROGRAMMING             | 5-5   |

| 5.3.2  | 2 DISKETTE DRIVE CONNECTOR               | 5-7   |

| 5.4    | SERIAL INTERFACE                         | 5-8   |

| 5.4.1  | 1 RS-232 INTERFACE                       | 5-8   |

| 5.4.2  |                                          |       |

| 5.5 PA    | RALLEL INTERFACE                                       |            |

|-----------|--------------------------------------------------------|------------|

| 5.5.1     | STANDARD PARALLEL PORT MODE                            | 5-10       |

| 5.5.2     | ENHANCED PARALLEL PORT MODE                            | 5-11       |

| 5.5.3     | EXTENDED CAPABILITIES PORT MODE                        | 5-11       |

| 5.5.4     | PARALLEL INTERFACE PROGRAMMING                         | 5-11       |

| 5.5.5     | PARALLEL INTERFACE CONNECTOR                           |            |

| 5.6 KE    | YBOARD/POINTING DEVICE INTERFACE                       | 5-14       |

| 5.6.1     | KEYBOARD INTERFACE OPERATION                           |            |

| 5.6.2     | POINTING DEVICE INTERFACE OPERATION                    |            |

| 5.6.3     | KEYBOARD/POINTING DEVICE INTERFACE PROGRAMMING         |            |

| 5.6.4     | KEYBOARD/POINTING DEVICE INTERFACE CONNECTOR           |            |

| 5.7 UN    | IVERSAL SERIAL BUS INTERFACE                           | 5-20       |

| 5.7.1     | USB DATA FORMATS                                       |            |

| 5.7.2     | USB PROGRAMMING                                        |            |

| 5.7.3     | USB CONNECTOR                                          |            |

| 5.7.4     | USB CABLE DATA                                         |            |

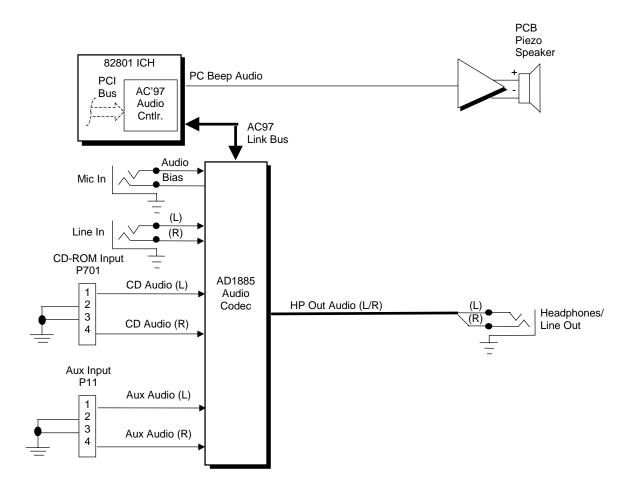

| 5.8 AU    | DIO SUBSYSTEM                                          |            |

| 5.8.1     | FUNCTIONAL ANALYSIS                                    |            |

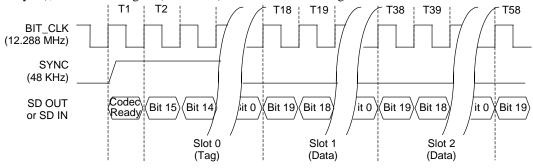

| 5.8.2     | AC97 AUDIO CONTROLLER                                  |            |

| 5.8.3     | AC97 LINK BUS                                          |            |

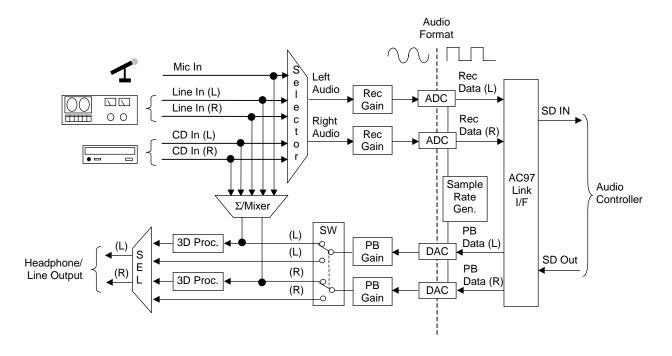

| 5.8.4     | AUDIO CODEC                                            |            |

| 5.8.5     | AUDIO PROGRAMMING                                      |            |

| 5.8.6     | AUDIO SPECIFICATIONS                                   |            |

| 5.9 NE    | TWORK SUPPORT                                          |            |

| 5.9.1     | PCI VER. 2.2 SUPPORT                                   |            |

| 5.9.2     | ALERT-ON-LAN SUPPORT                                   |            |

| 5.9.3     | REMOTE SYSTEM ALERT SUPPORT                            | 5-32       |

|           |                                                        |            |

|           |                                                        |            |

| CHAPTER ( | 6 EMBEDDED GRAPHICS SUBSYSTEM                          | •••••      |

| c 1 DI    | FRODUCTION                                             | <i>c</i> 1 |

|           |                                                        |            |

| 6.1.1     | FEATURE SUMMARY5-BASED GRAPHICS FUNCTIONAL DESCRIPTION |            |

|           |                                                        |            |

| 6.2.1     | DISPLAY MODES                                          |            |

|           | S-BASED GRAPHICS PROGRAMMING                           |            |

|           | ONITOR POWER MANAGEMENT CONTROL                        |            |

|           | ONITOR CONNECTOR                                       |            |

| 6.6 UP    | GRADING 815-BASED GRAPHICS                             | 6-6        |

|           |                                                        |            |

|           |                                                        |            |

| CHAPTER 7 | 7 POWER SUPPLY AND DISTRIBUTION                        | •••••      |

| 7 1 INT   | FRODUCTION                                             | 7.1        |

|           | FRODUCTIONWER SUPPLY ASSEMBLY/CONTROL                  |            |

|           |                                                        |            |

| 7.1.1     | POWER SUPPLY ASSEMBLY                                  |            |

| 7.1.2     | POWER CONTROL                                          |            |

|           | WER DISTRIBUTION                                       |            |

| 7.2.1     | 3.3/5/12 VDC DISTRIBUTION                              |            |

| 7.2.2     | LOW VOLTAGE DISTRIBUTION                               | 7-7<br>7   |

| / 4 21/   |                                                        |            |

| CHAPT | ER 8 BIOS ROM                                             | ••••• |

|-------|-----------------------------------------------------------|-------|

| 8.1   | INTRODUCTION                                              |       |

| 8.2   | ROM FLASHING                                              | 8-2   |

| 8.2   |                                                           |       |

| 8.2   | .2 CHANGEABLE SPLASH SCREEN                               | 8-3   |

| 8.3   | BOOT FUNCTIONS                                            | 8-4   |

| 8.3   |                                                           |       |

| 8.3   | 3.2 NETWORK BOOT (F12) SUPPORT                            | 8-4   |

| 8.3   | 3.3 MEMORY DETECTION AND CONFIGURATION                    | 8-5   |

| 8.3   | 3.4 BOOT ERROR CODES                                      | 8-5   |

| 8.4   | SETUP UTILITY                                             | 8-6   |

| 8.5   | CLIENT MANAGEMENT FUNCTIONS                               | 8-12  |

| 8.5   | 5.1 SYSTEM ID AND ROM TYPE                                | 8-14  |

| 8.5   | 5.2 EDID RETRIEVE                                         | 8-14  |

| 8.5   | TEMPERATURE STATUS                                        | 8-15  |

| 8.5   |                                                           |       |

| 8.6   | PNP SUPPORT                                               | 8-15  |

| 8.6   | 5.1 SMBIOS                                                | 8-16  |

| 8.7   | POWER MANAGEMENT FUNCTIONS                                | 8-17  |

| 8.7   | 1.1 INDEPENDENT PM SUPPORT                                | 8-17  |

| 8.7   |                                                           |       |

| 8.7   | APM 1.2 SUPPORT                                           | 8-19  |

| 8.8   | USB LEGACY SUPPORT                                        | 8-23  |

| A. AP | PPENDIX A ERROR MESSAGES AND CODES                        |       |

| A.1   | INTRODUCTION                                              |       |

| A.2   | BEEP/KEYBOARD LED CODES                                   |       |

| A.3   | POWER-ON SELF TEST (POST) MESSAGES                        |       |

| A.4   | SYSTEM ERROR MESSAGES (1xx-xx)                            |       |

| A.5   | MEMORY ERROR MESSAGES (2xx-xx)                            |       |

| A.6   | KEYBOARD ERROR MESSAGES (30x-xx)                          |       |

| A.7   | PRINTER ERROR MESSAGES (4xx-xx)                           |       |

| A.8   | VIDEO (GRAPHICS) ERROR MESSAGES (5xx-xx)                  |       |

| A.9   | DISKETTE DRIVE ERROR MESSAGES (6xx-xx)                    |       |

| A.10  | ~ ( )                                                     |       |

| A.11  |                                                           |       |

| A.12  | SYSTEM STATUS ERROR MESSAGES (16xx-xx)                    |       |

| A.13  |                                                           |       |

| A.14  | , ,                                                       |       |

| A.15  |                                                           |       |

| A.16  |                                                           |       |

| A.17  |                                                           |       |

| A.18  | NETWORK INTERFACE ERROR MESSAGES (60xx-xx)                |       |

| A.19  | SCSI INTERFACE ERROR MESSAGES (65xx-xx, 66xx-xx, 67xx-xx) |       |

| A.20  | POINTING DEVICE INTERFACE ERROR MESSAGES (8601-xx)        | A-11  |

| APPEN      | NDIX B ASCII CHARACTER SET                      |     |

|------------|-------------------------------------------------|-----|

| B.1        | INTRODUCTION                                    | B-1 |

|            |                                                 |     |

| APPEN      | NDIX C KEYBOARD                                 |     |

| C.1        | INTRODUCTION                                    |     |

| C.2        | KEYSTROKE PROCESSING                            |     |

| C.         | 2.1 PS/2-TYPE KEYBOARD TRANSMISSIONS            |     |

| C.         | 2.2 USB-TYPE KEYBOARD TRANSMISSIONS             |     |

| C.         | 2.3 KEYBOARD LAYOUTS                            |     |

| C.         | 2.4 KEYS                                        |     |

| C.         | 2.5 KEYBOARD COMMANDS                           |     |

|            | 2.6 SCAN CODES                                  |     |

| C.3        | CONNECTORS                                      |     |

|            | NDIX D COMPAQ/NVIDIA VANTA LT AGP GRAPHICS CARD |     |

| D.1        | INTRODUCTION                                    |     |

| D.2        | FUNCTIONAL DESCRIPTION                          |     |

| D.3        | DISPLAY MODES                                   |     |

| D.4        | SOFTWARE SUPPORT INFORMATION                    |     |

| D.5        | POWER MANAGEMENT AND CONSUMPTIONCONNECTORS      |     |

| D.6        | 6.1 MONITOR CONNECTOR                           |     |

| D.         | 0.1 MONITOR CONNECTOR                           | D-3 |

| APPEN      | NDIX E COMPAQ/NVIDIA M64 GRAPHICS CARD          |     |

| E.1        | INTRODUCTION                                    |     |

| E.1<br>E.2 | FUNCTIONAL DESCRIPTION                          |     |

| E.2<br>E.3 | DISPLAY MODES                                   |     |

| E.3<br>E.4 | SOFTWARE SUPPORT INFORMATION                    |     |

| E.5        | MONITOR CONTROL                                 |     |

| E.6        | CONNECTORS                                      |     |

|            | 6.2 MONITOR CONNECTOR                           |     |

| ٠.٠        |                                                 |     |

# **LIST OF FIGURES**

|                   | PAQ DESKPRO EX SERIES PERSONAL COMPUTERS WITH MONITORS                |      |

|-------------------|-----------------------------------------------------------------------|------|

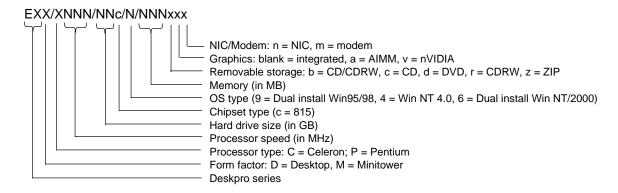

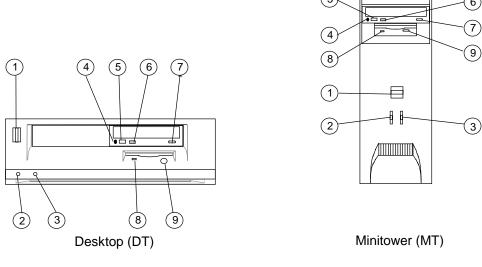

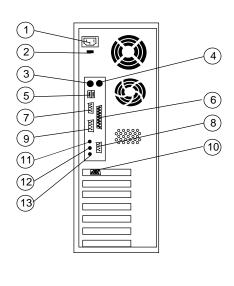

| FIGURE 2–2. COM   | PAQ DESKPRO EX SERIES, FRONT VIEWS                                    | 2-5  |

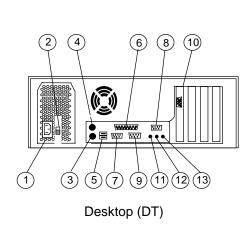

| FIGURE 2–3. COM   | PAQ DESKPRO EX SERIES, REAR VIEWS                                     | 2-6  |

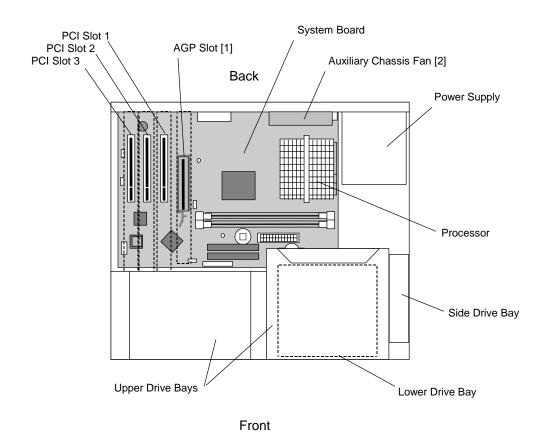

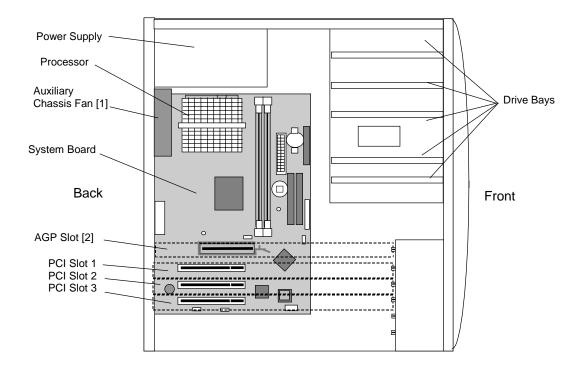

| FIGURE 2–4. COMI  | PAQ DESKPRO EX DESKTOP (DT) CHASSIS LAYOUT, TOP VIEW                  | 2-7  |

|                   | PAQ DESKPRO EX MINITOWER (MT) CHASSIS LAYOUT, SIDE VIEW               |      |

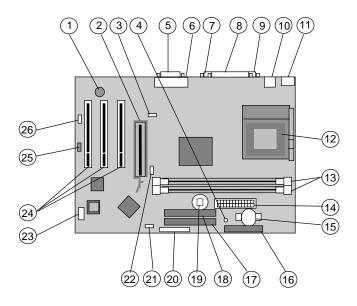

| FIGURE 2–6. SYST  | TEM BOARD LAYOUT                                                      | 2-9  |

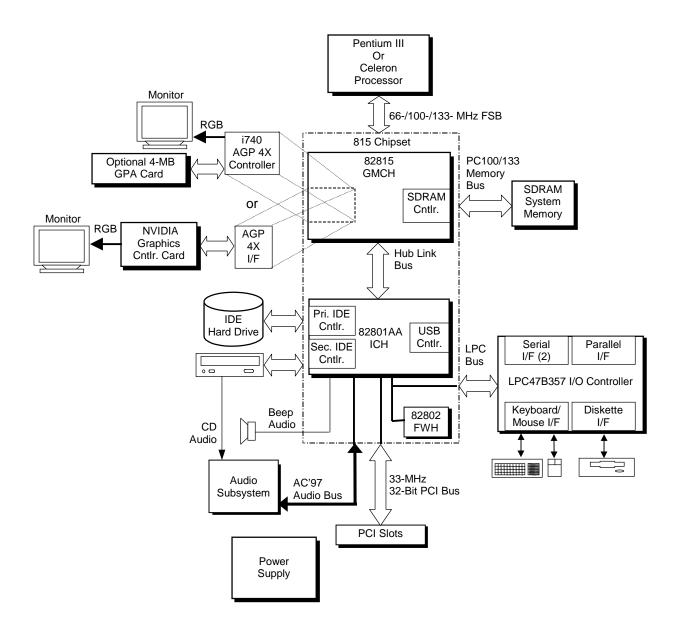

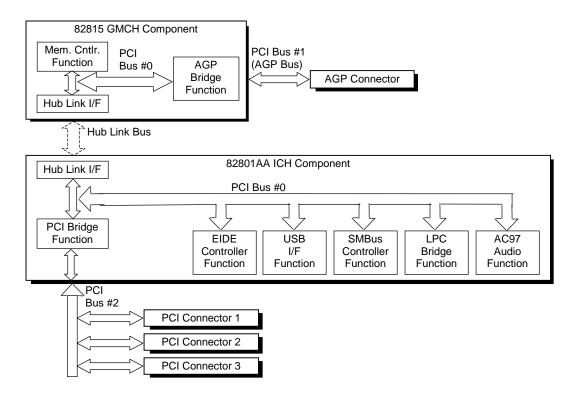

| FIGURE 2–7. COMP  | AQ DESKPRO EX ARCHITECTURE, BLOCK DIAGRAM                             | 2-11 |

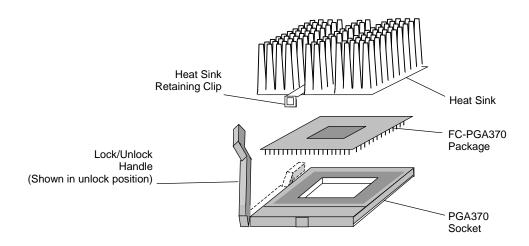

|                   | ESSOR ASSEMBLY AND MOUNTING                                           |      |

|                   |                                                                       |      |

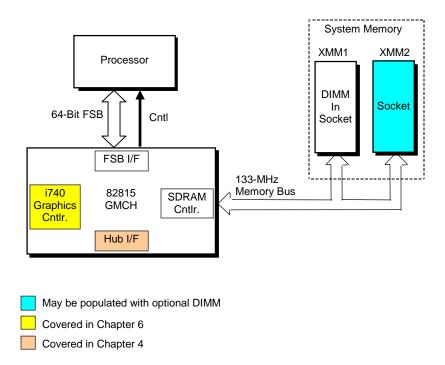

| FIGURE 3–1. PROC  | ESSOR/MEMORY SUBSYSTEM ARCHITECTURE                                   | 3-1  |

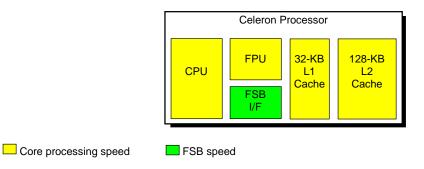

| FIGURE 3–2. CELE  | RON PROCESSOR INTERNAL ARCHITECTURE                                   | 3-2  |

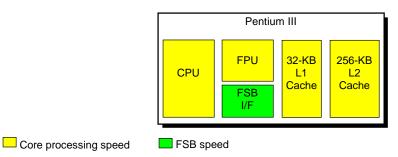

| FIGURE 3–3. PENT  | IUM III PROCESSOR INTERNAL ARCHITECTURE                               | 3-3  |

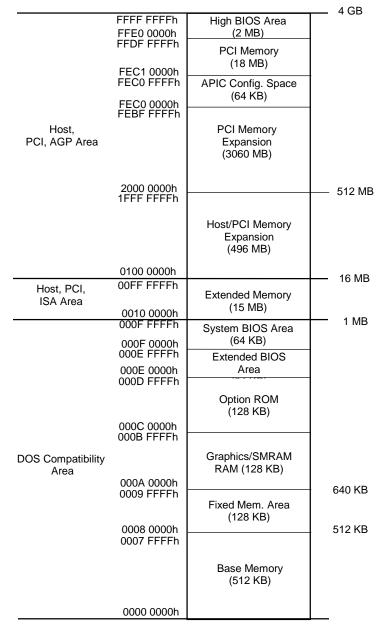

| FIGURE 3–4. SYST  | EM MEMORY MAP                                                         | 3-7  |

|                   |                                                                       |      |

|                   | US DEVICES AND FUNCTIONS                                              |      |

|                   | IGURATION CYCLE                                                       |      |

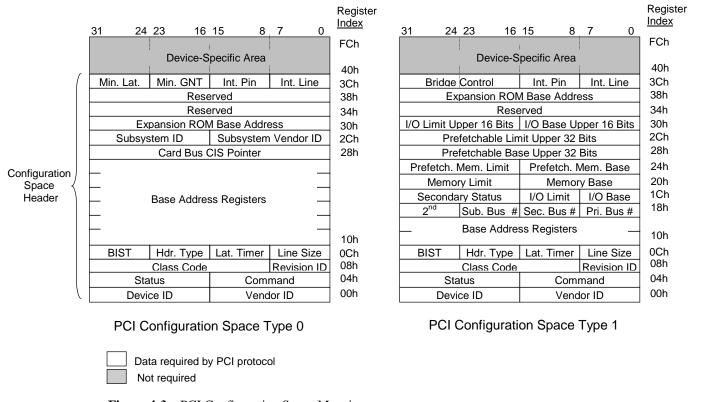

|                   | CONFIGURATION SPACE MAPPING                                           |      |

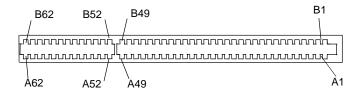

|                   | SUS CONNECTOR (32-BIT TYPE)                                           |      |

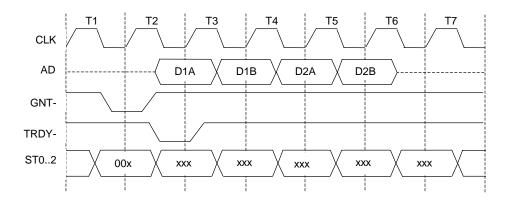

|                   | 1X Data Transfer (Peak Transfer Rate: 266 MB/s)                       |      |

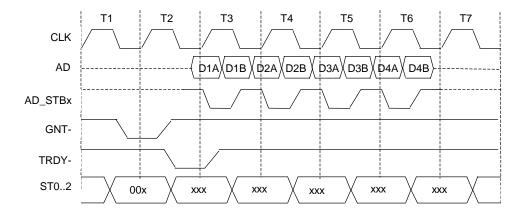

| FIGURE 4-6. AGP   | 2X Data Transfer (Peak Transfer Rate: 532 MB/s)                       | 4-12 |

| FIGURE 4-7. AGP   | 4X DATA TRANSFER (PEAK TRANSFER RATE: 1064 MB/s)                      | 4-12 |

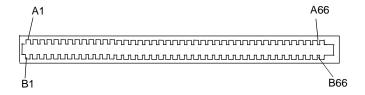

| FIGURE 4-8. UNIVE | ERSAL AGP BUS CONNECTOR                                               | 4-14 |

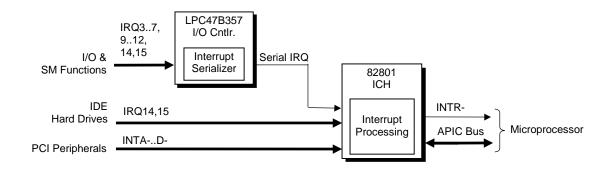

| FIGURE 4-9. MASK  | ABLE INTERRUPT PROCESSING, BLOCK DIAGRAM                              | 4-15 |

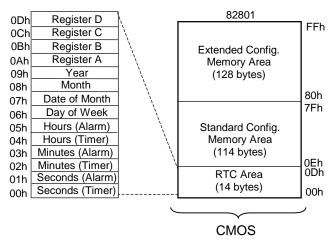

| FIGURE 4-10. CON  | FIGURATION MEMORY MAP                                                 | 4-23 |

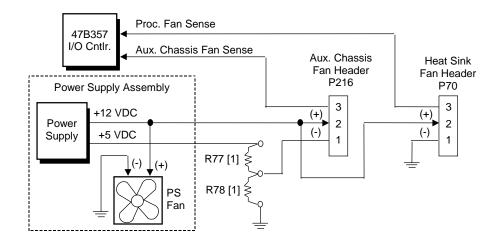

| FIGURE 4-11. FAN  | CONTROL BLOCK DIAGRAM                                                 | 4-37 |

|                   |                                                                       |      |

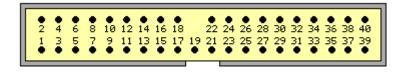

|                   | PRIMARY IDE CONNECTOR (ON SYSTEM BOARD)                               |      |

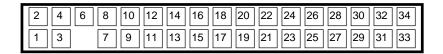

|                   | N DISKETTE DRIVE CONNECTOR.                                           |      |

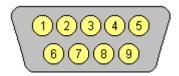

|                   | L INTERFACE CONNECTOR (MALE DB-9 AS VIEWED FROM REAR OF CHASSIS)      |      |

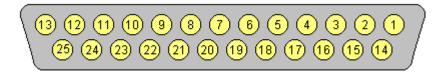

|                   | LEL INTERFACE CONNECTOR (FEMALE DB-25 AS VIEWED FROM REAR OF CHASSIS) |      |

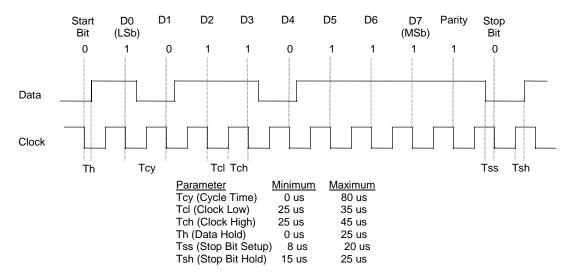

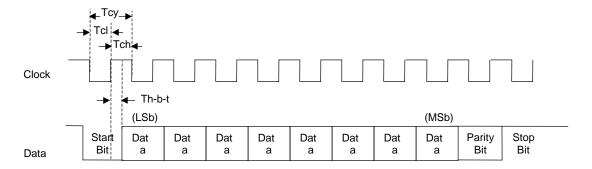

|                   | TO-KEYBOARD TRANSMISSION OF CODE EDH, TIMING DIAGRAM                  |      |

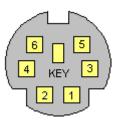

|                   | OARD OR POINTING DEVICE INTERFACE CONNECTOR                           |      |

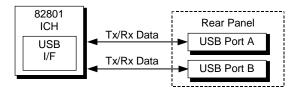

|                   | /F, Block Diagram                                                     |      |

|                   | PACKET FORMATS                                                        |      |

|                   | ERSAL SERIAL BUS CONNECTOR                                            |      |

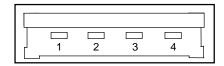

|                   | IO SUBSYSTEM FUNCTIONAL BLOCK DIAGRAM                                 |      |

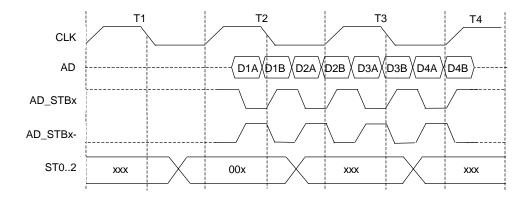

|                   | 97 LINK BUS PROTOCOL                                                  |      |

| FIGURE 5-12. AD1  | 885 AUDIO CODEC FUNCTIONAL BLOCK DIAGRAM                              | 5-27 |

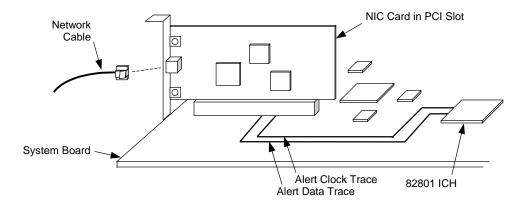

| FIGURE 5-13. AOL  | IMPLEMENTATION (GENERIC REPRESENTATION)                               | 5-31 |

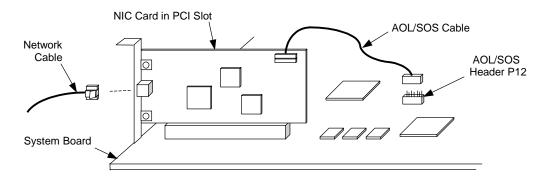

| FIGURE 5-14. REM  | OTE SENSE ALERT IMPLEMENTATION (GENERIC REPRESENTATION)               | 5-32 |

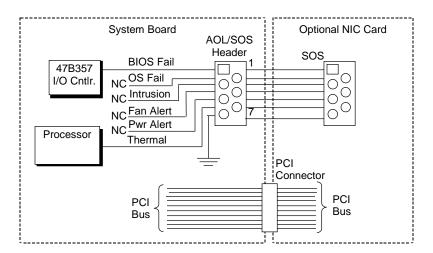

| FIGURE 5-15. RSA  | LOGIC, BLOCK DIAGRAM                                                  | 5-32 |

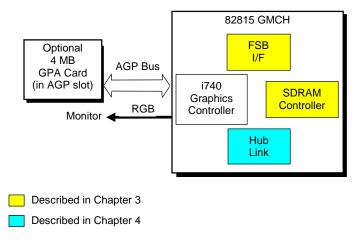

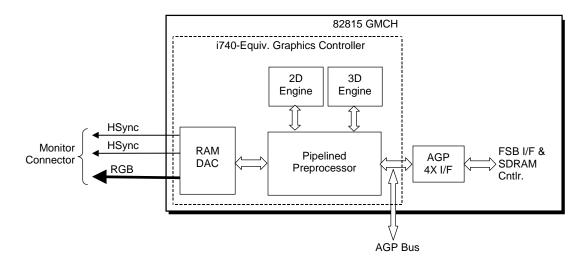

| FIGURE 6-1. 815E- | BASED GRAPHICS, BLOCK DIAGRAM                                         | 6-2  |

| FIGURE 6-2. 82815 | GMCH INTEGRATED GRAPHICS SUBSYSTEM                                    | 6-3  |

| _                 |                                                                       |      |

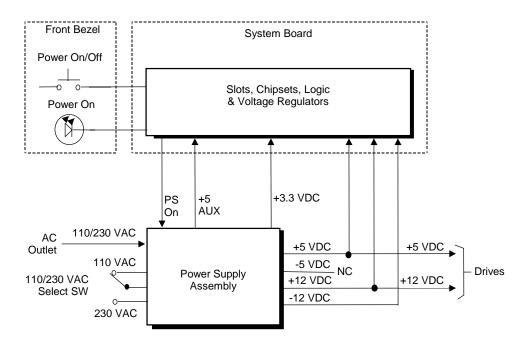

|                   | R DISTRIBUTION AND CONTROL, BLOCK DIAGRAM                             |      |

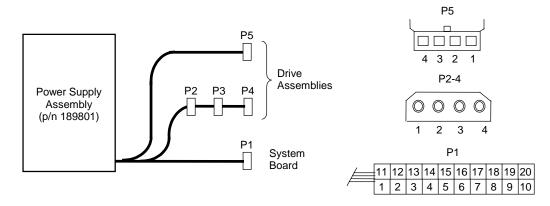

|                   | PRO EX DT POWER CABLE DIAGRAM                                         |      |

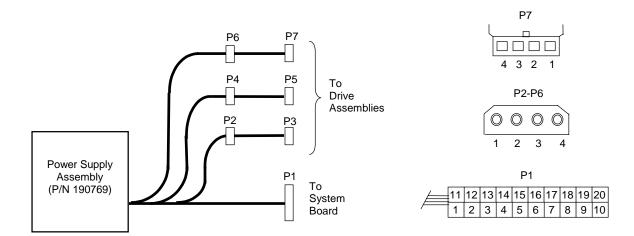

|                   | PRO EX MT POWER CABLE DIAGRAM                                         |      |

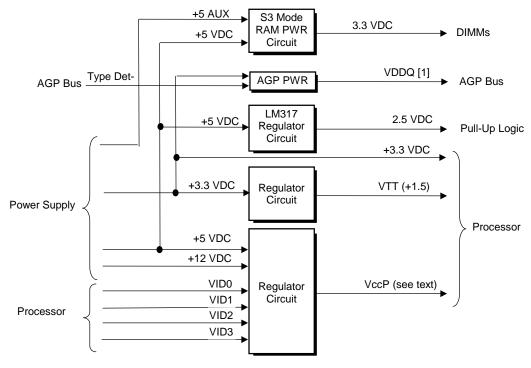

|                   | VOLTAGE SUPPLY AND DISTRIBUTION DIAGRAM                               |      |

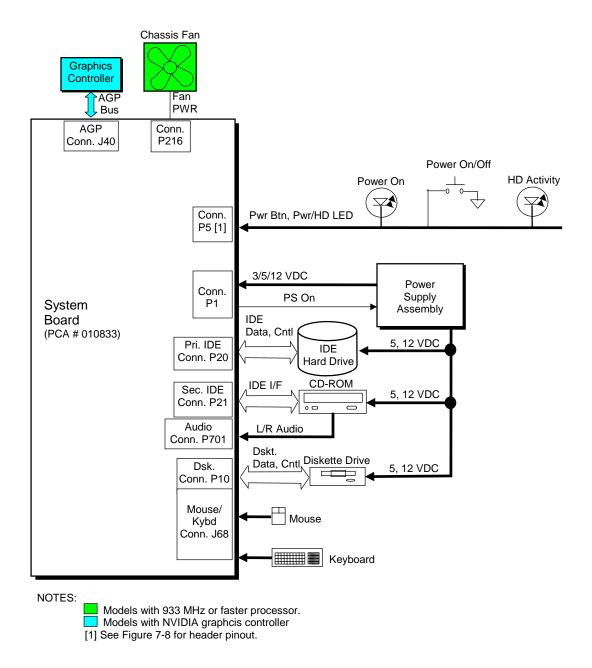

| FIGURE 7–5. SIGNA | AL DISTRIBUTION DIAGRAM (TYPICAL CONFIGURATION)                       | 7-8  |

| FIGURE 7–6. HEAD  | DER PINOUTS.                                                          | 7-9  |

| FIGURE B–1. | ASCII CHARACTER SET                                              | B-1  |

|-------------|------------------------------------------------------------------|------|

|             |                                                                  |      |

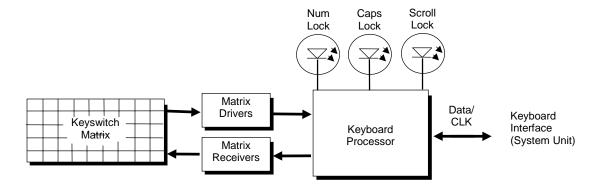

| FIGURE C-1. | KEYSTROKE PROCESSING ELEMENTS, BLOCK DIAGRAM                     | C-2  |

|             | PS/2 KEYBOARD-TO-SYSTEM TRANSMISSION, TIMING DIAGRAM             |      |

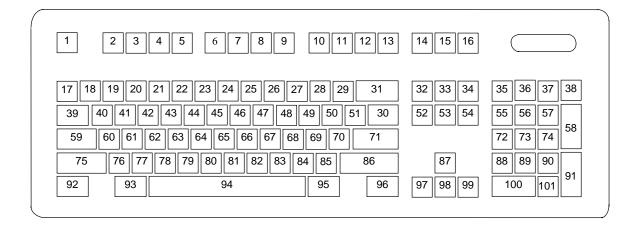

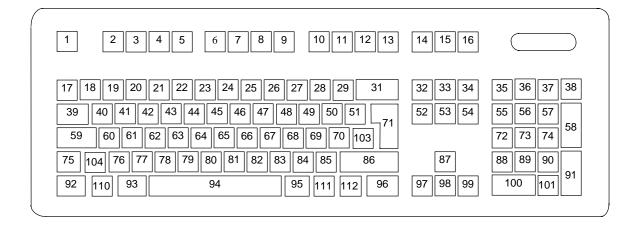

| FIGURE C-3. | U.S. ENGLISH (101-KEY) KEYBOARD KEY POSITIONS                    | C-5  |

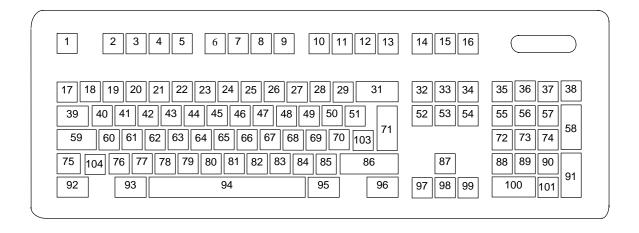

| FIGURE C-4. | NATIONAL (102-KEY) KEYBOARD KEY POSITIONS                        | C-5  |

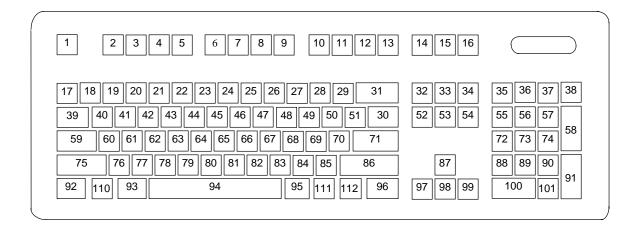

| FIGURE C-5. | U.S. ENGLISH WINDOWS (101W-KEY) KEYBOARD KEY POSITIONS           | C-6  |

| FIGURE C-6. | NATIONAL WINDOWS (102W-KEY) KEYBOARD KEY POSITIONS               | C-6  |

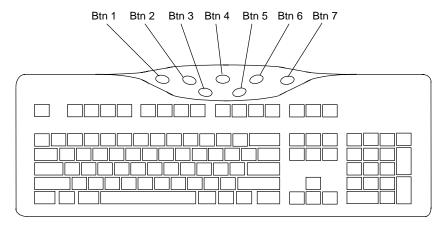

| FIGURE C-7. | 7-BUTTON EASY ACCESS KEYBOARD LAYOUT                             | C-7  |

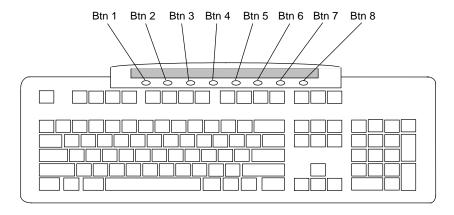

| FIGURE C-8. | 8-BUTTON EASY ACCESS KEYBOARD LAYOUT                             | C-7  |

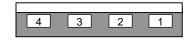

| FIGURE C-9. | PS/2 KEYBOARD CABLE CONNECTOR (MALE)                             | C-16 |

|             | . USB KEYBOARD CABLE CONNECTOR (MALE)                            |      |

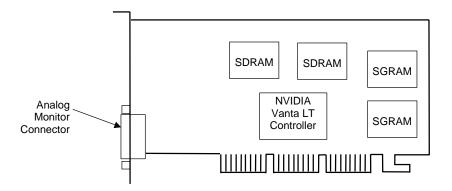

| FIGURE D-1. | COMPAQ/NVIDIA VANTA LT AGP GRAPHICS CARD (P/N 192174-002) LAYOUT | D-1  |

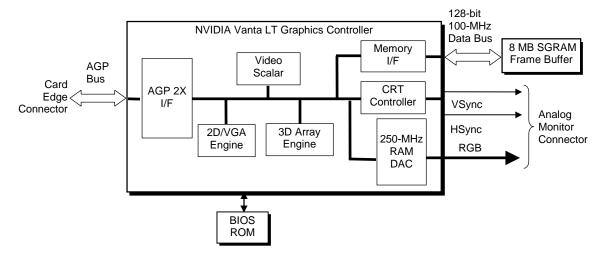

| FIGURE D-2. | COMPAQ/NVIDIA VANTA LT GRAPHICS CARD BLOCK DIAGRAM               | D-2  |

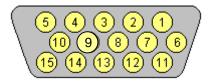

| FIGURE D-3. | VGA MONITOR CONNECTOR, (FEMALE DB-15, AS VIEWED FROM REAR)       | D-5  |

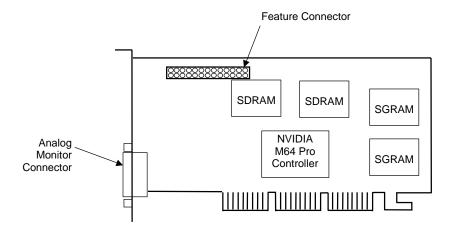

| FIGURE E–1. | COMPAQ/NVIDIA M64 AGP GRAPHICS CARD LAYOUT (COMPAQ P/N 179250)   | E-1  |

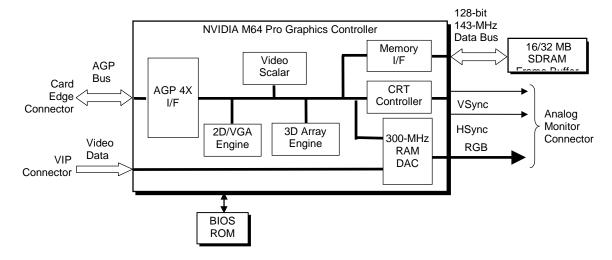

|             | COMPAQ/NVIDIA M64 AGP GRAPHICS CARD BLOCK DIAGRAM                |      |

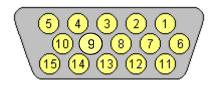

|             | VGA MONITOR CONNECTOR, (FEMALE DB-15, AS VIEWED FROM REAR)       |      |

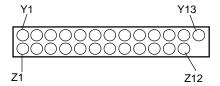

|             | VIDEO INTERFACE CONNECTOR (26-PIN HEADER)                        |      |

# LIST OF TABLES

| TABLE 1–1. ACRONYMS AND ABBREVIATIONS                                 | 1-3  |

|-----------------------------------------------------------------------|------|

| TABLE 2-1. FEATURE DIFFERENCE MATRIX                                  | 2-2  |

| TABLE 2-2. CHIPSET COMPARISON                                         |      |

| TABLE 2-3. SUPPORT COMPONENT FUNCTIONS                                | 2-14 |

| TABLE 2-4. GRAPHICS SUBSYSTEM COMPARISON                              | 2-16 |

| TABLE 2-5. ENVIRONMENTAL SPECIFICATIONS                               | 2-17 |

| TABLE 2-6. ELECTRICAL SPECIFICATIONS                                  | 2-17 |

| TABLE 2-7. PHYSICAL SPECIFICATIONS                                    | 2-18 |

| TABLE 2-8. DISKETTE DRIVE SPECIFICATIONS                              | 2-18 |

| TABLE 2-9. 48x CD-ROM DRIVE SPECIFICATIONS                            | 2-19 |

| TABLE 2-10. HARD DRIVE SPECIFICATIONS                                 | 2-19 |

| Table 3–1. Celeron Processor Statistical Comparison                   | 3-2  |

| TABLE 3–2. PENTIUM III PROCESSOR STATISTICAL COMPARISON               | 3-3  |

| TABLE 3–3. SPD ADDRESS MAP (SDRAM DIMM)                               |      |

| TABLE 3–4. HOST/PCI BRIDGE CONFIGURATION REGISTERS (GMCH, FUNCTION 0) | 3-8  |

| Table 4-1. PCI Device Configuration Access                            | 4-4  |

| TABLE 4-2. SYSTEM BOARD PCI DEVICE IDENTIFICATION                     | 4-5  |

| TABLE 4-3. PCI BUS MASTERING DEVICES                                  | 4-6  |

| TABLE 4-4. LPC BRIDGE CONFIGURATION REGISTERS (ICH, FUNCTION 0)       | 4-8  |

| TABLE 4-5. PCI BUS CONNECTOR PINOUT                                   | 4-9  |

| TABLE 4-6. PCI/AGP BRIDGE CONFIGURATION REGISTERS (MCH, FUNCTION 1)   | 4-13 |

| TABLE 4-7. AGP BUS CONNECTOR PINOUT                                   |      |

| TABLE 4-8. MASKABLE INTERRUPT PRIORITIES AND ASSIGNMENTS              |      |

| TABLE 4-9. MASKABLE INTERRUPT CONTROL REGISTERS                       |      |

| TABLE 4-10. DEFAULT DMA CHANNEL ASSIGNMENTS                           |      |

| TABLE 4-11. DMA PAGE REGISTER ADDRESSES                               |      |

| TABLE 4-12. DMA CONTROLLER REGISTERS                                  | 4-21 |

| TABLE 4-13. CLOCK GENERATION AND DISTRIBUTION                         | 4-22 |

| TABLE 4-14. CONFIGURATION MEMORY (CMOS) MAP                           |      |

| TABLE 4-15. SYSTEM BOOT/ROM FLASH STATUS LED INDICATIONS              |      |

| TABLE 4-16. SYSTEM OPERATIONAL STATUS LED INDICATIONS                 |      |

| TABLE 4-17. SYSTEM I/O MAP                                            |      |

| TABLE 4-18. 82801 ICH GPIO REGISTER UTILIZATION.                      |      |

| TABLE 4-19 LPC47B357 CONTROL REGISTERS                                |      |

| TABLE 4-20. LPC47B357 GPIO REGISTER UTILIZATION                       |      |

| TABLE 5–1. IDE PCI CONFIGURATION REGISTERS                            | 5-2  |

| TABLE 5–2. IDE BUS MASTER CONTROL REGISTERS                           | 5-2  |

| TABLE 5–3. 40-PIN PRIMARY IDE CONNECTOR PINOUT                        | 5-3  |

| TABLE 5–4. DISKETTE DRIVE CONTROLLER CONFIGURATION REGISTERS          | 5-5  |

| TABLE 5–5. DISKETTE DRIVE INTERFACE CONTROL REGISTERS                 | 5-5  |

| TABLE 5–6. 34-PIN DISKETTE DRIVE CONNECTOR PINOUT                     | 5-7  |

| TABLE 5–7. DB-9 SERIAL CONNECTOR PINOUT                               | 5-8  |

| TABLE 5–8. SERIAL INTERFACE CONFIGURATION REGISTERS                   |      |

| TABLE 5–9. SERIAL INTERFACE CONTROL REGISTERS.                        |      |

| TABLE 5–10. PARALLEL INTERFACE CONFIGURATION REGISTERS                |      |

| TABLE 5–11. PARALLEL INTERFACE CONTROL REGISTERS                      |      |

| TABLE 5–12. DB-25 PARALLEL CONNECTOR PINOUT                           |      |

|                                                                       |      |

| Table 5–13. 8042-To-Keyboard Commands                                |      |

|----------------------------------------------------------------------|------|

| TABLE 5–14. KEYBOARD INTERFACE CONFIGURATION REGISTERS               | 5-16 |

| TABLE 5–15. CPU COMMANDS TO THE 8042                                 | 5-18 |

| TABLE 5–16. KEYBOARD/POINTING DEVICE CONNECTOR PINOUT                | 5-19 |

| TABLE 5–17. USB INTERFACE CONFIGURATION REGISTERS                    | 5-22 |

| TABLE 5–18. USB CONTROL REGISTERS                                    | 5-22 |

| TABLE 5–19. USB CONNECTOR PINOUT                                     | 5-23 |

| TABLE 5–20. USB CABLE LENGTH DATA                                    | 5-23 |

| TABLE 5–21. AC'97 AUDIO CONTROLLER PCI CONFIGURATION REGISTERS       | 5-28 |

| TABLE 5–22. AC'97 AUDIO CODEC CONTROL REGISTERS                      | 5-28 |

| TABLE 5–23. AUDIO SUBSYSTEM SPECIFICATIONS                           | 5-29 |

| TABLE 5–24. AOL EVENTS                                               | 5-30 |

| TABLE 5–25. REMOTE SYSTEM ALERT EVENTS                               | 5-33 |

| Table 6-1. Intel Graphics Display Modes                              | 6-4  |

| TABLE 6-2. 815-BASED GRAPHICS CONTROLLER PCI CONFIGURATION REGISTERS | 6-5  |

| TABLE 6-3. MONITOR POWER MANAGEMENT CONDITIONS                       | 6-5  |

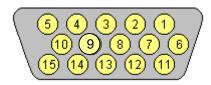

| TABLE 6-4. DB-15 MONITOR CONNECTOR PINOUT                            | 6-6  |

| TABLE 8-1. BOOT BLOCK CODES                                          | 8-2  |

| TABLE 8-2. BOOT ERROR CODES.                                         | 8-5  |

| TABLE 8-3. SETUP UTILITY FUNCTIONS.                                  |      |

| TABLE 8-4. CLIENT MANAGEMENT FUNCTIONS (INT15)                       |      |

| TABLE 8-5. PNP BIOS FUNCTIONS                                        |      |

| TABLE 8-6. APM BIOS FUNCTIONS                                        | 8-20 |

| TABLE A-1. BEEP/KEYBOARD LED CODES                                   | A-1  |

| TABLE A-2. POWER-ON SELF TEST (POST) MESSAGES                        | A-2  |

| TABLE A-3. SYSTEM ERROR MESSAGES                                     |      |

| TABLE A-4. MEMORY ERROR MESSAGES                                     | A-4  |

| TABLE A-5. KEYBOARD ERROR MESSAGES                                   | A-4  |

| TABLE A-6. PRINTER ERROR MESSAGES                                    | A-5  |

| TABLE A-7. VIDEO (GRAPHICS) ERROR MESSAGES                           | A-5  |

| TABLE A–8. DISKETTE DRIVE ERROR MESSAGES                             | A-6  |

| TABLE A-9. SERIAL INTERFACE ERROR MESSAGES                           | A-6  |

| TABLE A-10. SERIAL INTERFACE ERROR MESSAGES                          | A-7  |

| TABLE A-11. SYSTEM STATUS ERROR MESSAGES                             | A-8  |

| TABLE A-12. HARD DRIVE ERROR MESSAGES                                | A-8  |

| TABLE A-13. HARD DRIVE ERROR MESSAGES                                | A-9  |

| TABLE A-14. HARD DRIVE MESSAGES                                      | A-9  |

| TABLE A-15. AUDIO ERROR MESSAGES                                     |      |

| TABLE A-16. DVD/CD-ROM DRIVE ERROR MESSAGES                          | A-10 |

| TABLE A-17. NETWORK INTERFACE ERROR MESSAGES                         | A-10 |

| TABLE A-18. SCSI INTERFACE ERROR MESSAGES                            |      |

| TABLE A-19. POINTING DEVICE INTERFACE ERROR MESSAGES                 | A-11 |

| TABLE C-1. KEYBOARD-TO-SYSTEM COMMANDS                               | C-11 |

| TABLE C-2. KEYBOARD SCAN CODES                                       | C-12 |

| TABLE D-1. NVIDIA VANTA LT 2D GRAPHICS DISPLAY MODES                 | D-3  |

| TABLE D-2. MONITOR POWER MANAGEMENT CONDITIONS                       |      |

| TABLE D-3. DB-15 MONITOR CONNECTOR PINOUT                            | D-5  |

| TABLE E-1. | NVIDIA M64 2D Graphics Display Modes  | .E-3 |

|------------|---------------------------------------|------|

| TABLE E-2. | MONITOR POWER MANAGEMENT CONDITIONS   | .E-4 |

| TABLE E-3. | DB-15 MONITOR CONNECTOR PINOUT        | .E-5 |

| TABLE E-4. | MULTIMEDIA INTERFACE CONNECTOR PINOUT | .E-6 |

# Chapter 1 INTRODUCTION

# 1.1 ABOUT THIS GUIDE

This guide provides technical information about the Compaq Deskpro EX Series of Personal Computers. This document includes information regarding system design, function, and features that can be used by programmers, engineers, technicians, and system administrators.

This guide and any applicable addendums are available online at the following location:

http://www.compaq.com/support/techpubs/technical reference guides/index.html

### 1.1.1 USING THIS GUIDE

The chapters of this guide primarily describe the hardware and firmware elements and primarily deal with the system board and the power supply assembly. The appendices contain general information about standard peripheral devices such as the keyboard.